Vertrauenswürdige Plattform-Chips

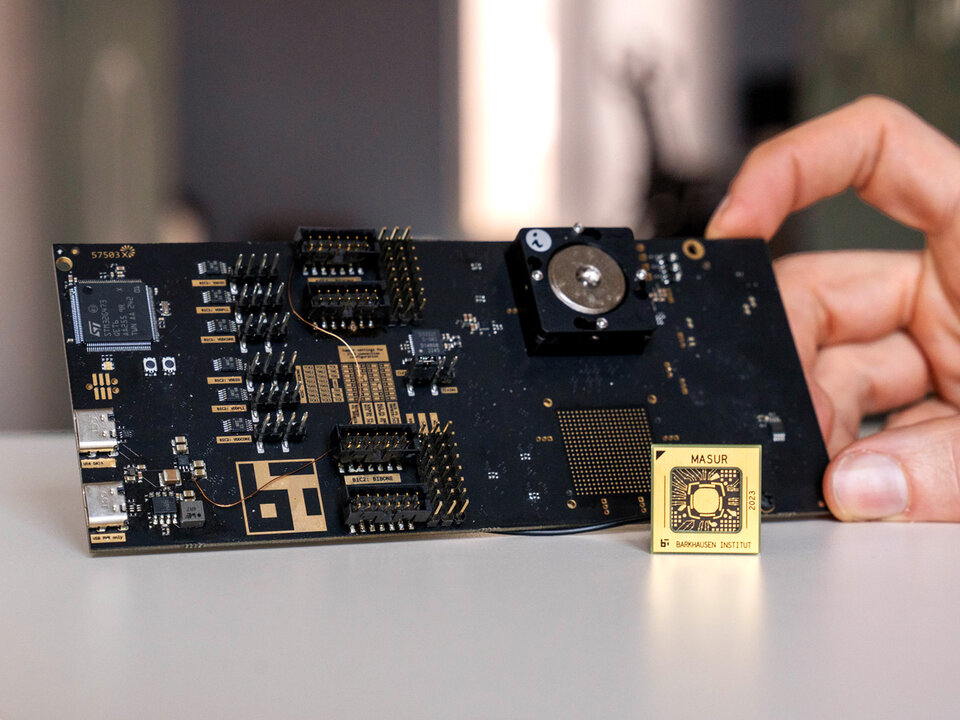

Das Barkhausen Institut (BI) entwickelt digitale Plattform-Chips, die das Herzstück moderner, intelligenter und vernetzter Elektronik bilden. In der Forschungsgruppe Scalable Computing Hardware werden sämtliche Schritte – von der Konzeption über das physikalische Chipdesign bis zur funktionalen Inbetriebnahme – intern umgesetzt. Dazu gehört auch die Entwicklung industrietauglicher, standardisierter Packages sowie spezieller Trägerplatinen für den Betrieb.

Die digitalen Plattform-Chips des BI sind zentrale Steuer- und Kommunikationseinheiten in unterschiedlichsten Anwendungen: Sie integrieren Prozessoren, Schnittstellen und Speicher und ermöglichen die Ausführung komplexer Aufgaben – etwa maschinelles Lernen, Echtzeitsteuerung oder KI-Funktionen – direkt im Gerät. Einsatzgebiete sind unter anderem Robotik, Automobiltechnik, Industrieautomation und moderne Sensorik.

Das BI verfügt über langjährige Erfahrung und Expertise in der Strukturierung, Entwicklung und Integration kundenspezifischer IP-Blöcke – vom KI-Beschleuniger über Sicherheitsmodule bis hin zu komplexen Multiprozessor-System-on-Chip-Architekturen (MPSoC). Über 50 erfolgreich umgesetzte Chipdesign-Projekte von Mitarbeitern und Mitarbeiterinnen des BI, darunter zahlreiche Industriekooperationen, belegen dieses Know-how. Test- und Evaluierungsphasen erfolgen vollständig im eigenen Labor.

Die entwickelten Plattform-Chips stehen für technologische Souveränität, Flexibilität und höchste Zuverlässigkeit – und sind ein entscheidender Baustein für eine unabhängige, wettbewerbsfähige und innovationsgetriebene Mikroelektronik in Deutschland und Europa.

Chips entwickelt am Barkhausen Institut

Die am Barkhausen Institut entwickelten Chips stehen für vertrauenswürdige Hardware im Bereich komplexer MPSoC-Architekturen. Sie sind speziell für sicherheitskritische Anwendungen wie Kommunikation, Sensorik und Industrieautomatisierung konzipiert.

Dank einer zeitnahen Fertigung und Inbetriebnahme können neue, kundenspezifische IP-Blöcke schnell in realem Silizium evaluiert werden. Die komplette Test- und Evaluierungsinfrastruktur befindet sich am Institut, was eine enge Rückkopplung zwischen Entwicklung und praktischer Validierung ermöglicht.

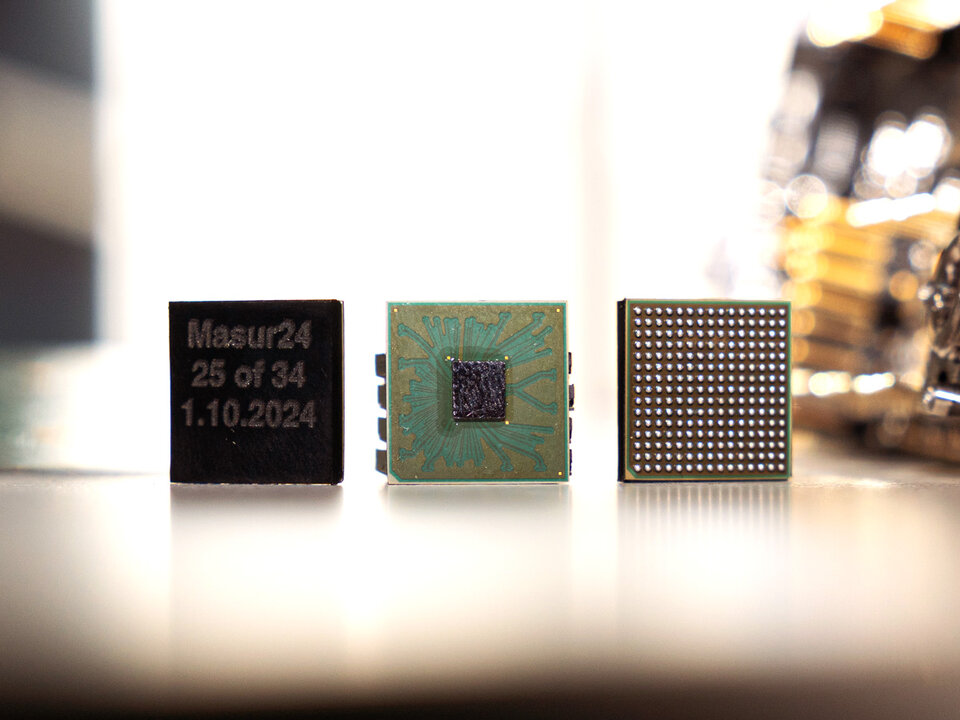

Die am Barkhausen Institut entwickelte Chip-Serie „Masur“ leiht sich ihren Namen von dem bekannten sächsischen Dirigenten Kurt Masur. Ein zentrales Merkmal der Masur-Chips ist die enge Integration des sicheren Betriebssystems M³ mit der Hardware. Interdisziplinäre Teams aus Hard- und Softwareentwicklung arbeiten dabei Hand in Hand, um höchste Sicherheits- und Zuverlässigkeitsstandards zu gewährleisten.

Kachel1

- Digitaler Multiprozessor Chip mit Fokus auf Ausführung von verteilten Anwendungen

- Vorlage für die sicherheitszentrierte Plattform-Chip-Line vom BI

- Kooperation zwischen Technischen Universität Dresden (TUD) und BI

- Resultat aus 15+ Jahre Chipentwicklung an der TUD

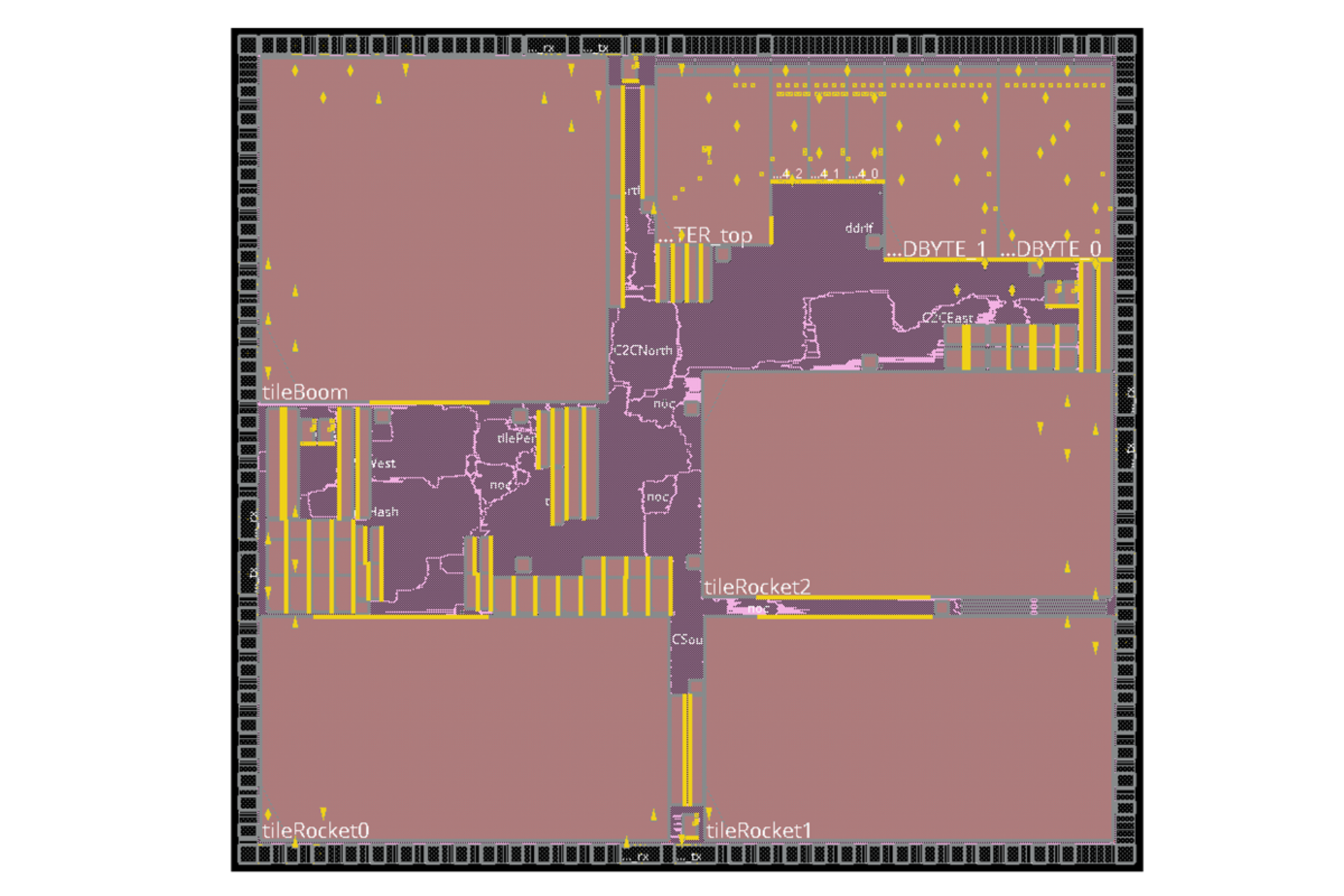

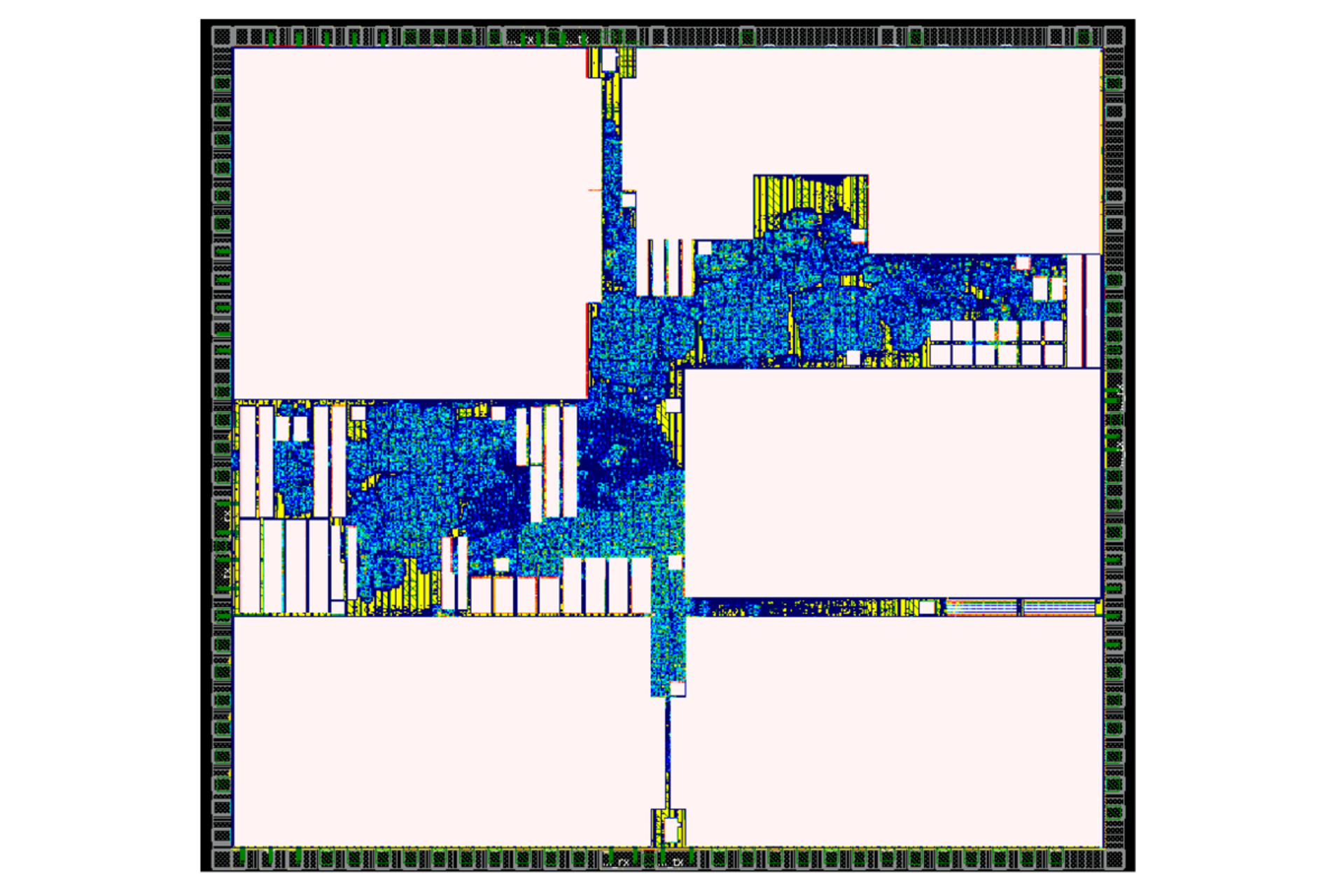

Masur23

- Übernahme des Kernteams für Chipentwicklung von der TUD

- Neuausrichtung der Kachel-Plattform hin zur sicherheitszentrierten Masur-Plattform

- Basiert auf Open Source RISC-V Prozessorkernen

- Erster Chip mit der am BI entwickelten Sicherheitskomponente Trusted Communication Unit (TCU)

- Fertigung im 22nm Technologieprozess bei GlobalFoundries in Dresden

- Laufzeit von Entwurf bis Test ca. 9-12 Monate

- Integration mehrerer Prozessoren mit Sicherheitsmechanismen auf einem Chip

Masur24

- Digitaler Plattform-Chip (System-on-Chip)

- Unterstützt das am BI von der Forschungsgruppe Composable Operating Systems entwickelte Betriebssystem M³, das auf Sicherheit durch isolierte Komponenten und verifizierbare Trusted Communication Units (TCU) setzt

- Fokus auf Sicherheitsforschung in Multiprozessor-Architekturen (MPSoC)

- Integration applikationsspezifischer Rechenmodule und Beschleuniger für kryptographische Algorithmen

- Integration eines Speicher-Interfaces zur Anbindung von externen DDR-Speicherchips

Masur25

- Weiterentwickelte digitale Chip-Generation

- Fokus auf Optimierung der Architektur und Integration spezieller IP-Blöcke zur Erhöhung der Sicherheit und Erweiterbarkeit

- Integration von Modulen externer Partner (Uni Tübingen) (KI-Beschleuniger, Kamera-Interface)

- Standalone-Betrieb; Starten des Chips ohne Hilfe eines Laborcomputers

Masur26 (in Arbeit)

- Optimierung der chipinternen Kommunikationsstrukturen; Verbesserungen am Network-on-Chip (NoC)

- Applikation der M³-Sicherheitskonzepte auf kohärente Caches

- Integration weiterer externer Module (TUD, …)

Masur27 (geplant)

- Optimierung des Datendurchsatzes sowohl im On-Chip-Netzwerk als auch über externe Schnittstellen (DDR, PCI, ...)

- Integration datenintensiver Beschleuniger, wie bspw. hoch-effiziente, leistungsstarke KI-Beschleuniger und Prozessoren für HPC-Netzwerkprotokolle

- Kooperation mit Analogdesignteam für die sichere Einbindung von mixed-signal Komponenten wie AD/DA-Wandler

Lehre

HW/SW Codesign for Digital Signal Processing (EuI-ET-E-HwSwD)

Dieser Kurs behandelt grundlegende Herausforderungen und Methoden der Implementierung von Hardware- und Softwareverarbeitung. Im Mittelpunkt stehen insbesondere die Design-Trade-offs und die Entwurfsmethoden des Co-Designs von Hardware- und Softwaresystemen, mit einem besonderen Schwerpunkt auf dem Hardware-Architekturdesign. Mit dem Übergang zu Nanometer-Technologien eröffnen sich umfangreiche Realisierungsmöglichkeiten, die einen besonderen Fokus auf Parallelverarbeitung und Multiprozessorsysteme erfordern.

Betreuender Dozent: Prof. Dr.-Ing. Gerhard Fettweis

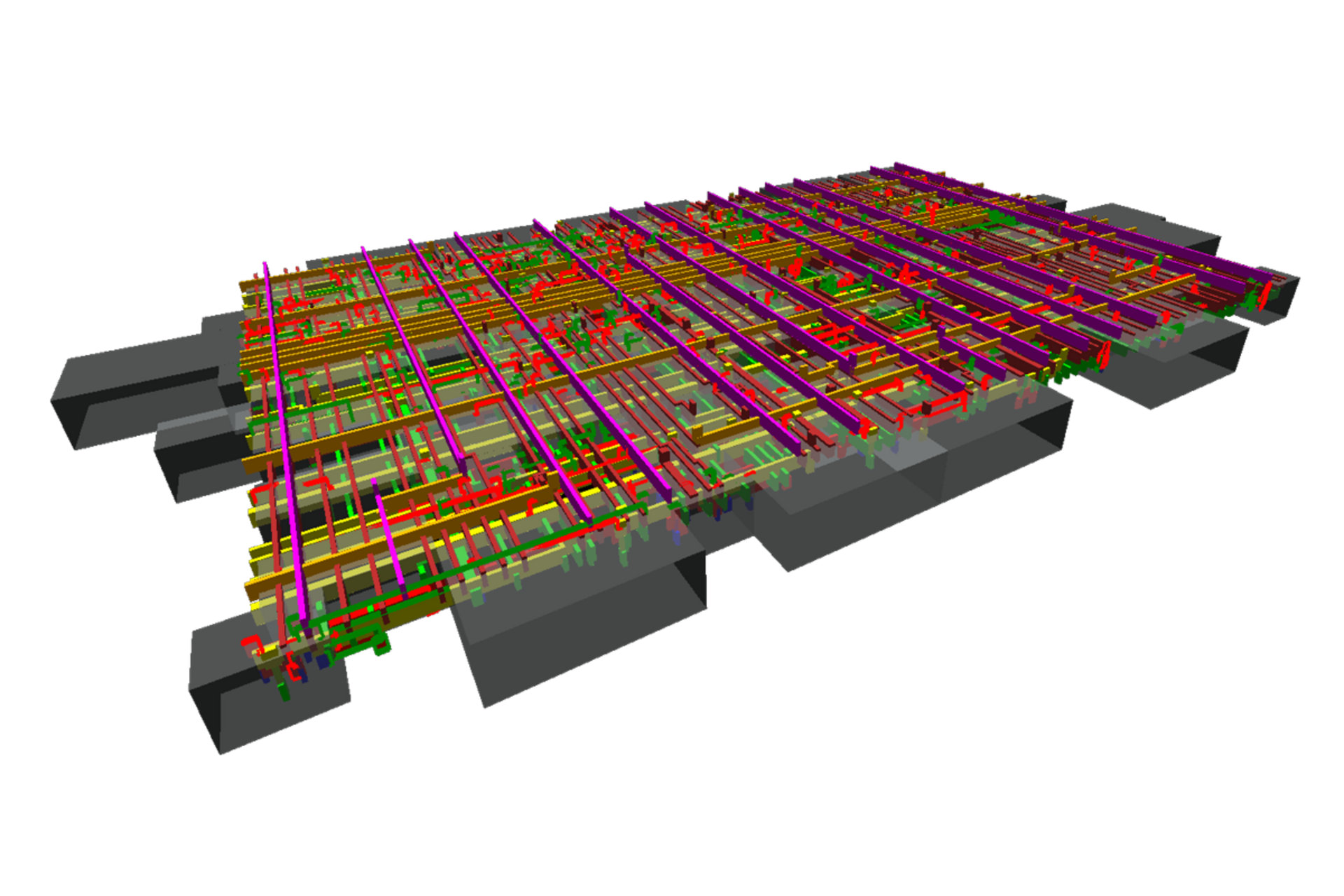

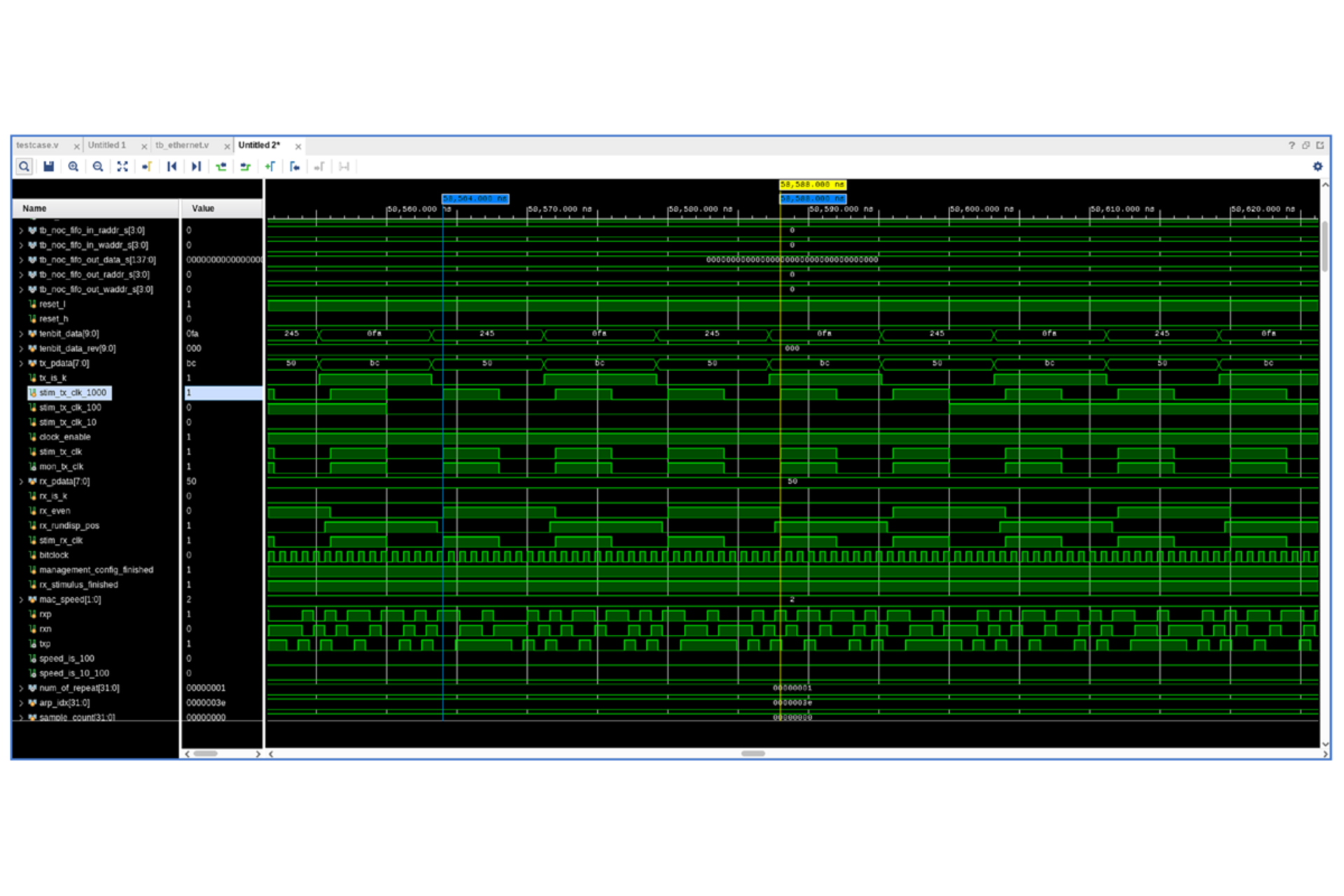

Physical Design (English only)

Physical design is an integral part of development of digital hardware. The content taught in this course will help the students to plan and execute implementations of systems like processors, advanced VLSI systems design and physical layers of communications.

Mikrokernkonstruktion

Diese Vorlesung konzentriert sich auf die aktuellen Entwicklungen im Bereich der Mikrokerne der zweiten Generation. Nach einer Einführung in Mikrokernel-basierte Betriebssysteme im Allgemeinen wird die Konstruktion des Mikrokernels selbst untersucht, indem z.B. die Interprozesskommunikation, Threads und Adressräume betrachtet werden. Die Übungen bieten praktische Erfahrung, indem sie den Studierenden die Möglichkeit geben, an einem abgespeckten Mikrokernel zu hacken. Schließlich werden in der Vorlesung mehrere Fallstudien von Mikrokernen vorgestellt, die im akademischen Bereich und in der Industrie eingesetzt werden.

Mikrokernbasierte Betriebssysteme

Diese Vorlesung behandelt verschiedene Aspekte und Konzepte der Konstruktion und Implementierung von mikrokernbasierten Betriebssystemen. Im ersten Teil führen wir grundlegende Mechanismen ein, die benötigt werden um effizient ein System auf einem Mikrokern zu konstruieren. Im zweiten Teil der Vorlesung stellen wir tatsächliche Systeme aufbauend auf diesen Konzepten vor. Obwohl wir die Mikrokern-Arbeiten der TU Dresden bevorzugt beleuchten, werden auch Alternativen betrachtet.