Trustworthy Platform Chips

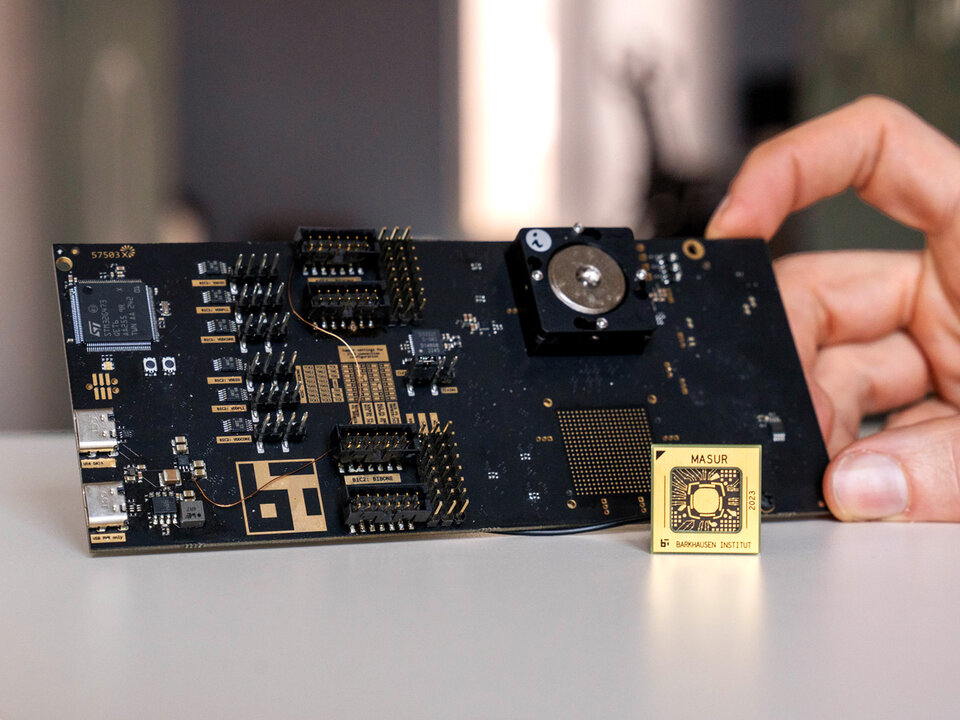

The Barkhausen Institut (BI) develops digital platform chips that form the core of modern, intelligent, and connected electronics. The Scalable Computing Hardware team covers every stage in-house - from concept and physical chip design to full system commissioning. This includes the development of industry-ready, standardized packages and dedicated carrier boards for operation.

BI’s digital platform chips serve as the control and communication center in a wide range of applications: they integrate processors, interfaces, and memory, enabling advanced tasks such as machine learning, real-time control, or AI directly on the device. Use cases span robotics, automotive, industrial automation, and advanced sensor systems.

The BI has extensive experience and expertise in structuring, developing, and integrating customer-specific IP blocks - ranging from AI accelerators and security modules to complex multiprocessor system-on-chip architectures (MPSoC). The researchers at BI draw on experience from more than 50 successfully completed chip design projects, including numerous industrial collaborations.

Platform chips developed at BI represent technological sovereignty, flexibility, and reliability. They are essential for a competitive, innovative, and independent microelectronics sector in Germany and Europe.

Chips Developed at the Barkhausen Institut

The chips developed at the Barkhausen Institut stand for trustworthy hardware in the field of complex Multiprocessor System-on-Chip (MPSoC) architectures. They are designed specifically for safety-critical applications such as communication, sensor technology, and industrial automation.

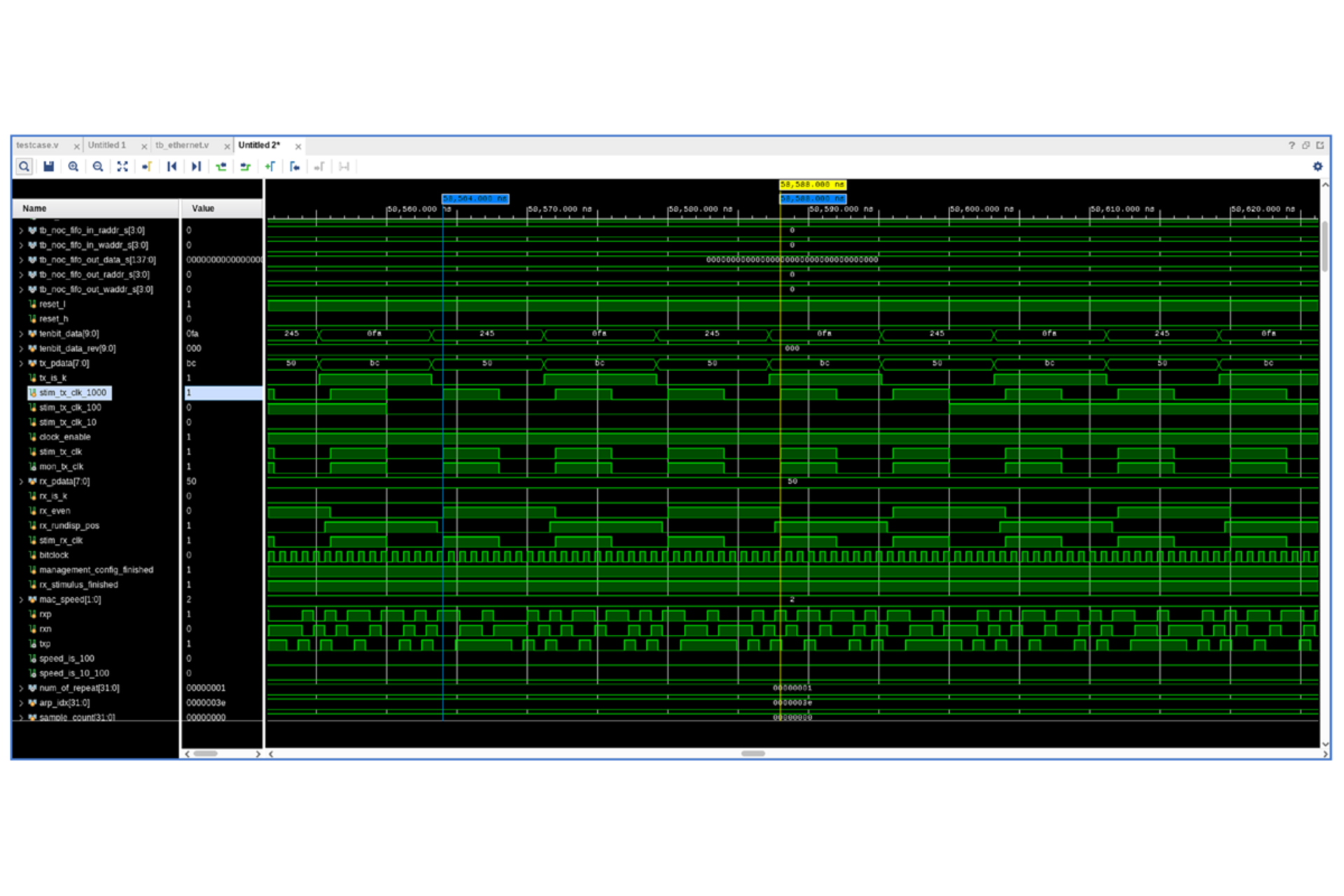

Thanks to fast fabrication and commissioning, new customer-specific IP blocks can be quickly evaluated in real silicon. The complete testing and evaluation infrastructure is located at the institute, enabling close feedback between development and practical validation.

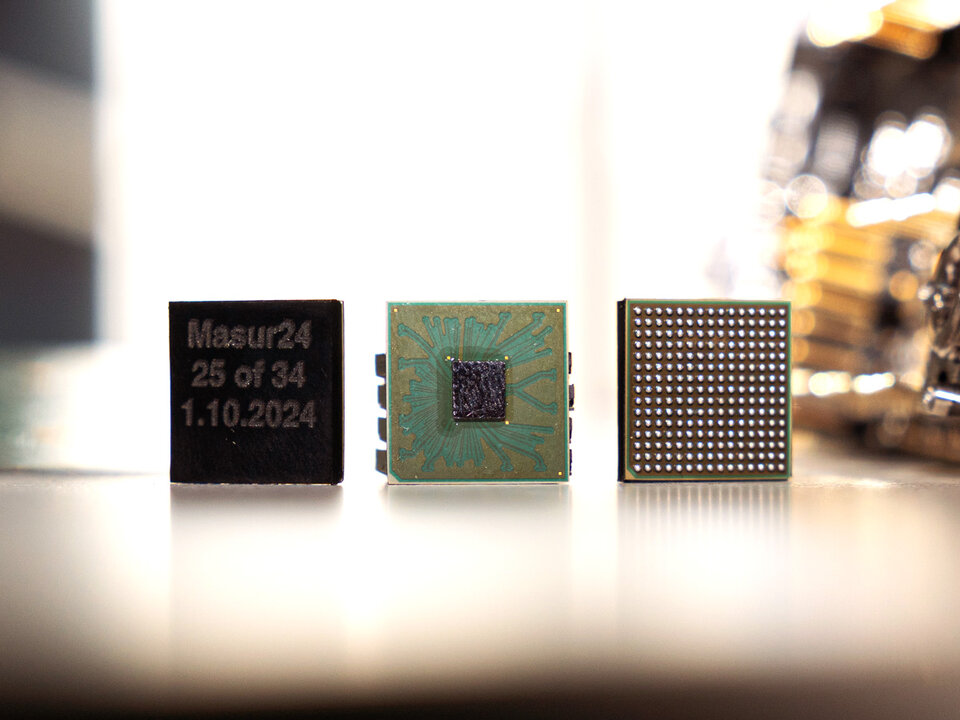

The “Masur” chip series developed at the Barkhausen Institut takes its name from Kurt Masur, the renowned conductor from Saxony. A key feature of the Masur chips is the close integration of the secure M³ operating system with the hardware. Interdisciplinary teams from hardware and software development work hand in hand to achieve the highest standards of security and reliability.

Kachel1

- Digital multiprocessor chip focused on executing distributed applications

- Template for the BI’s security-centric platform chip line

- Collaboration between TU Dresden (TUD) and BI

- Result of more than 15 years of chip development at TUD

Masur23

- Transfer of TUD’s core chip development team to BI

- Reorientation of the Kachel1 platform into the security-focused Masur platform

- Based on open-source RISC-V processor cores

- First chip featuring a BI-developed security component, the Trusted Communication Unit (TCU)

- Fabricated using GlobalFoundries’ 22nm technology in Dresden

- Design-to-test cycle of approx. 9-12 months

- Integration of multiple processors with security mechanisms on a single chip

Masur24

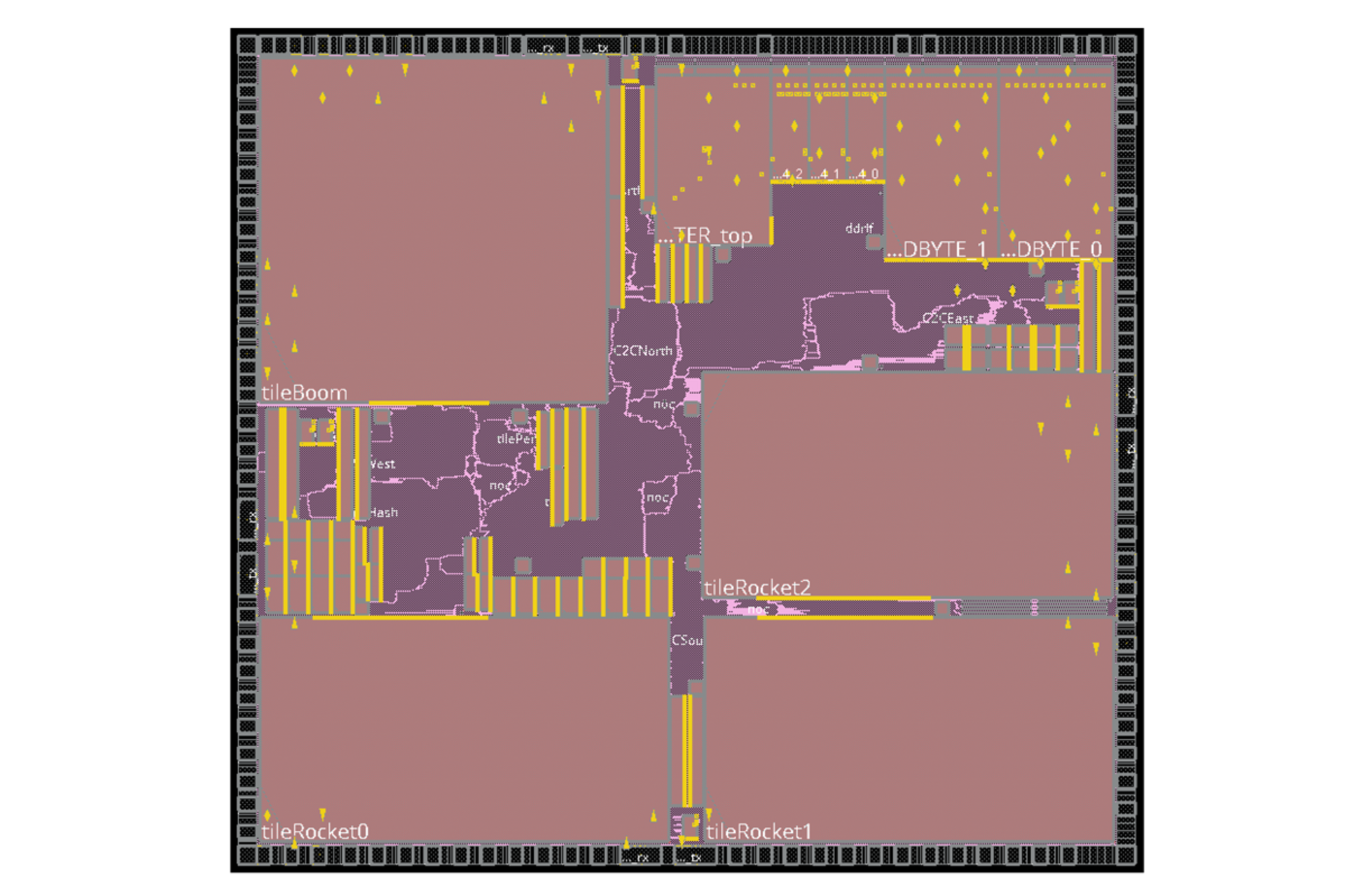

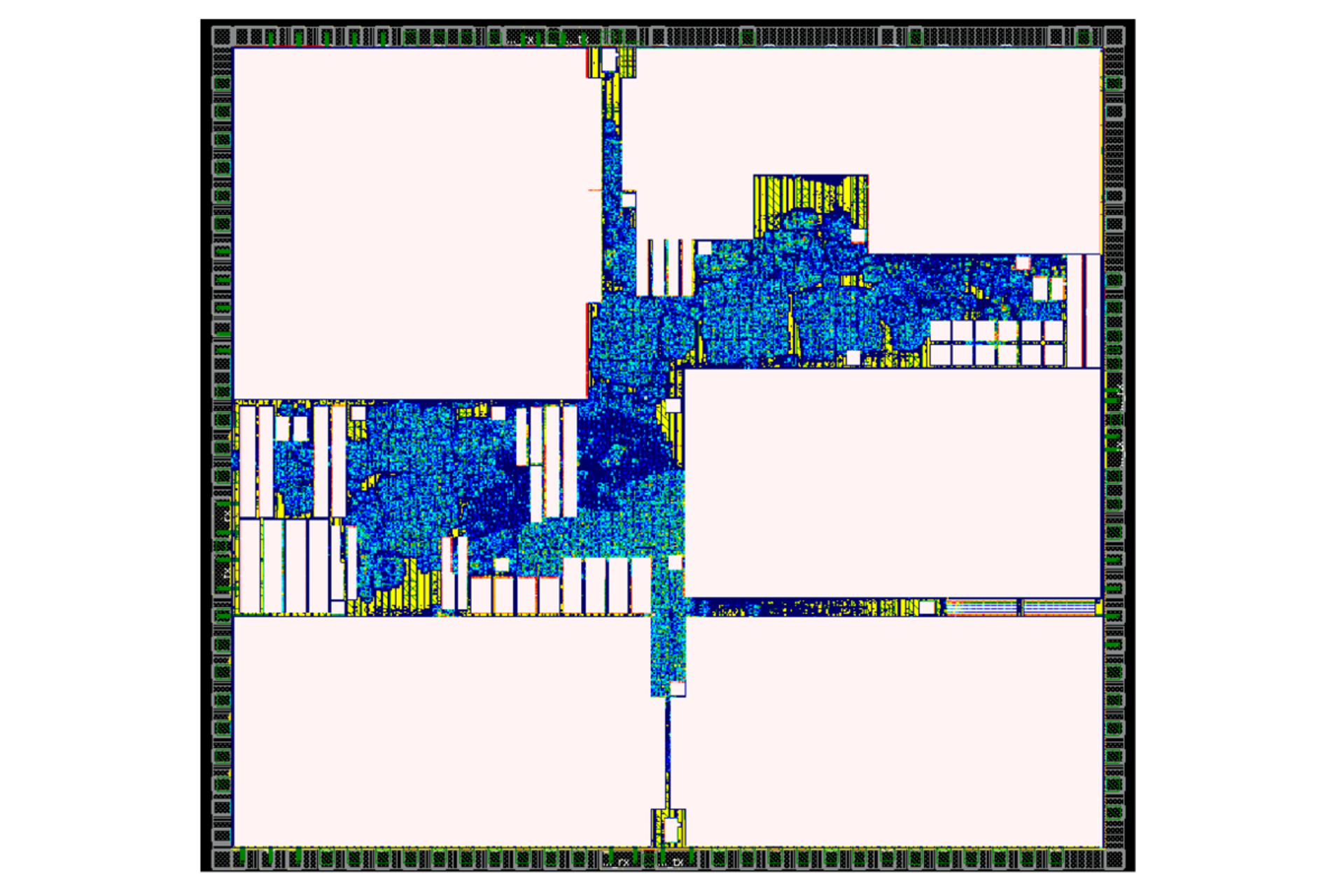

- Digital platform chip (System-on-Chip)

- Supports the M³ operating system developed at BI’s Composable Operating Systems research group, focusing on security through isolated components and verifiable Trusted Communication Units (TCU)

- Focus on security research in multiprocessor architectures (MPSoCs)

- Integration of application-specific compute modules and accelerators for cryptographic algorithms

- Integration of a memory interface for connecting external DDR memory chips

Masur25

- Advanced digital chip generation

- Focus on optimizing the architecture and integrating specialized IP blocks to increase security and scalability

- Integration of modules from external partners (University of Tübingen), such as AI accelerators and camera interfaces

- Standalone operation; capable of booting without assistance from a laboratory computer

Masur26 (in progress)

- Optimization of on-chip communication structures; improvements to the Network-on-Chip (NoC)

- Application of M³ security concepts to coherent caches

- Integration of additional external modules (TUD, …)

Masur27 (planned)

- Optimization of data throughput both in the on-chip network and across external interfaces (DDR, PCI, …)

- Integration of data-intensive accelerators, such as high-efficiency, high-performance AI accelerators and HPC network protocol processors

- Collaboration with the analog design team for secure integration of mixed-signal components such as ADC/DAC converters

Teaching

HW/SW Codesign for Digital Signal Processing (EuI-ET-E-HwSwD)

This course covers fundamental processing hardware and software implementation challenges and methodologies. In particular the design tradeoff and design methodologies of co-designing both, hardware as well as software systems are covered, with an emphasis on hardware architecture design. By moving into nano-scale devices very large-scale realization possibilities are enabled which requires a special emphasis to be given on parallel processing and multi-processor systems.

Supervising lecturer: Prof. Dr.-Ing. Gerhard Fettweis

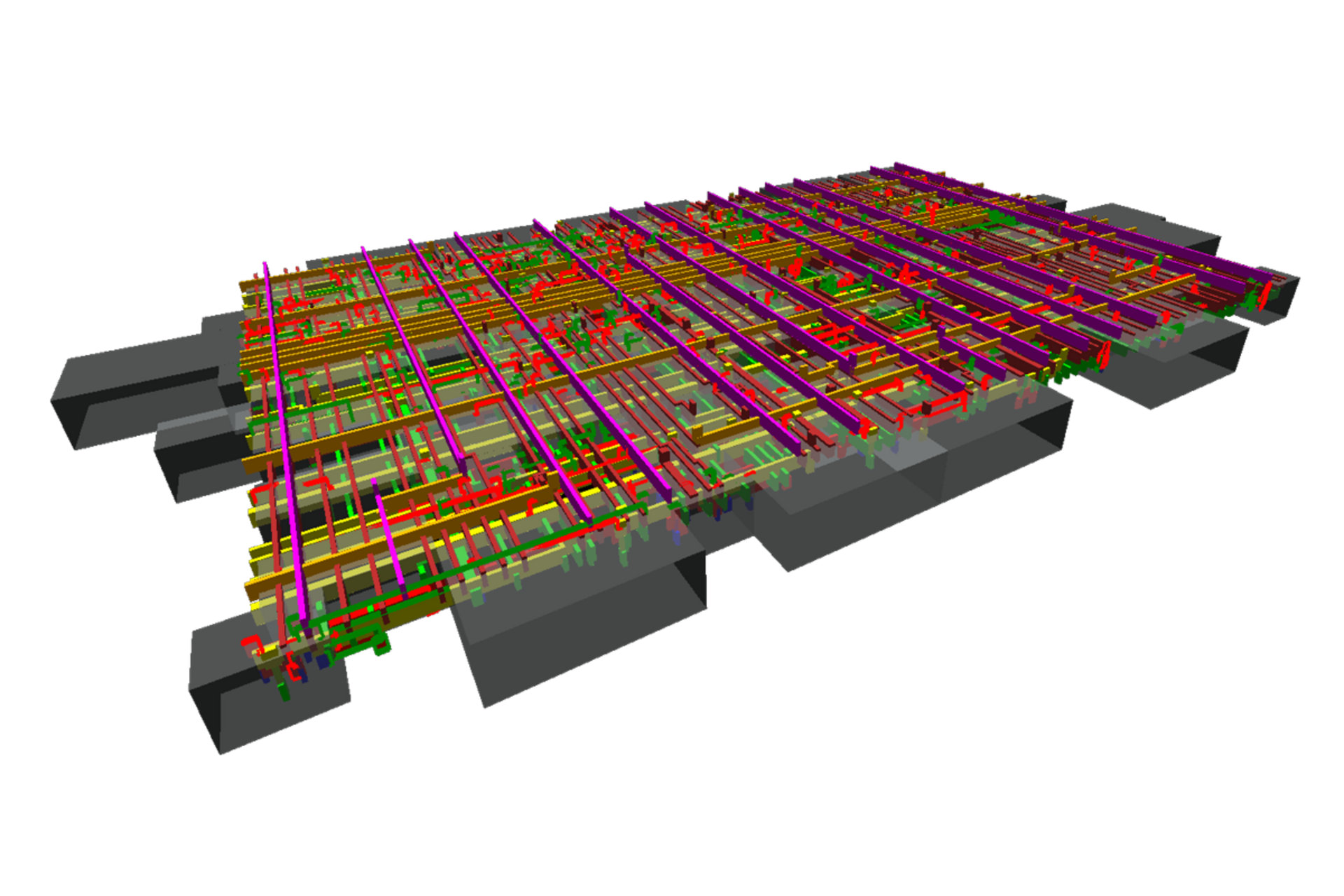

Physical Design (English only)

Physical design is an integral part of development of digital hardware. The content taught in this course will help the students to plan and execute implementations of systems like processors, advanced VLSI systems design and physical layers of communications.

Microkernel Construction

This lecture focuses on current developments in the area of 2nd generation microkernels. After introducing microkernel-based operating systems in general, it dives into the construction of the microkernel itself by looking at the design of, e.g., interprocess communication, threads, and address spaces. The exercises provide hands-on experience by allowing students to hack on a stripped-down microkernel. Finally, the lecture presents multiple case studies of microkernels used in academia and industry.

Microkernel-based Operating Systems

This lecture introduces various aspects and concepts regarding the construction and implementation of microkernel-based operating system. In the first part, we introduce fundamental mechanisms that are required for efficient construction of an operating system on top of a microkernel. In the second part of the lecture, we show you real systems that have been built using these concepts. While strongly focussing on the microkernel work done at TU Dresden, we also take a look at alternatives.