Analoge und Mixed-Signal-Funkchips

Das Barkhausen Institut (BI) entwickelt analoge und Mixed-Signal Funkchips als Grundlage für innovative und vertrauenswürdige Hardwarelösungen. Die Forschungsgruppe RF Design Enablement begleitet den gesamten Prozess – von der Schaltungsentwicklung über hochfrequenzoptimiertes Antennendesign bis hin zur physischen Realisierung (Layout-Erstellung) mit modernsten Halbleitertechnologien im Mikroelektronik-Cluster Silicon Saxony. Das Co-Design von Chipgehäusen und Leiterplatten (Package- und PCB-Design) ist präzise auf die anspruchsvollen Anforderungen analoger Hochfrequenz-Anwendungen abgestimmt.

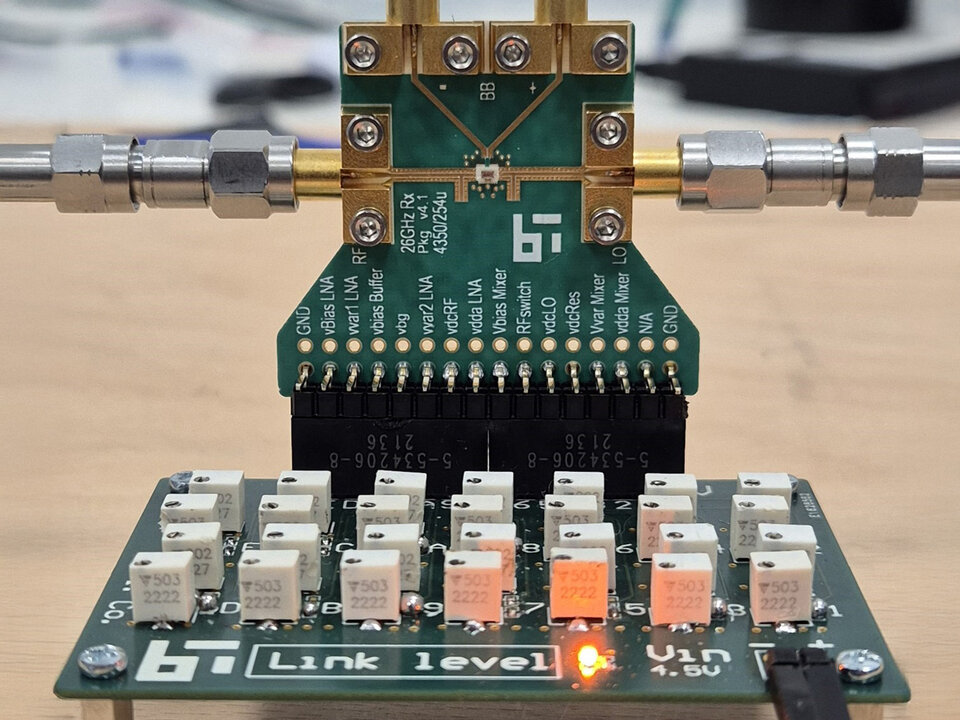

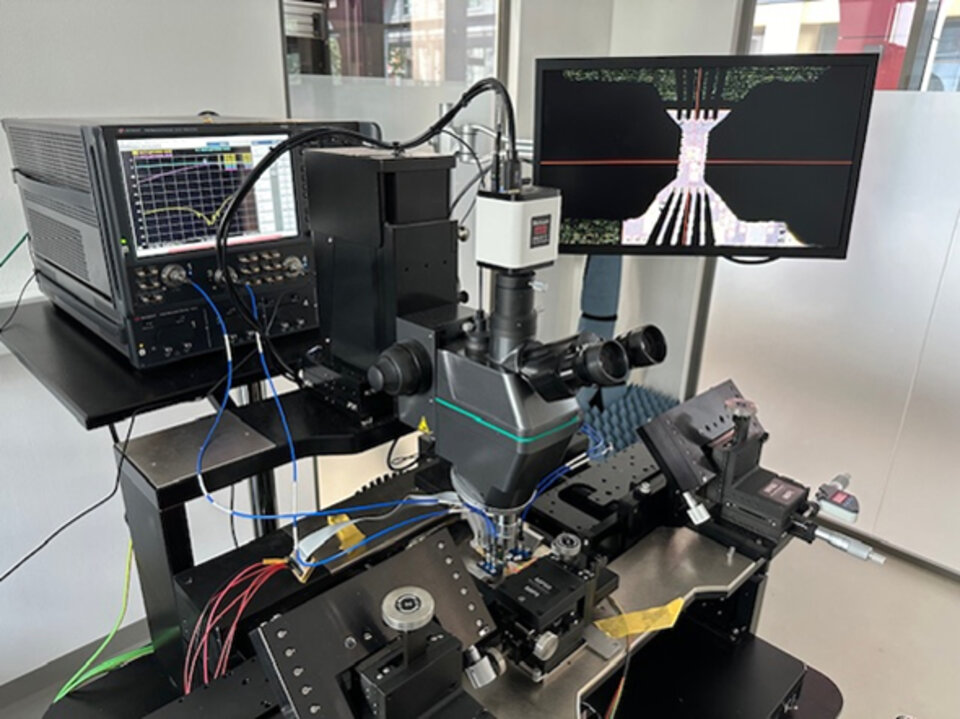

Nach der Fertigung erfolgen in den BI-Laboren umfassende Funktionstests, Charakterisierungen und Systemevaluierungen. Diese ermöglichen es, die Signalintegrität und die Interoperabilität einzelner Komponenten bereits vor der Integration ins Gesamtsystem detailliert zu analysieren – was potentielle Fehlerquellen minimiert und die Entwicklungsqualität steigert.

Die am BI entwickelten analogen und Mixed-Signal Funkchips kommen überall dort zum Einsatz, wo hochpräzise Signalverarbeitung und höchste Zuverlässigkeit gefragt sind – etwa in sicherheitskritischer Kommunikation, anspruchsvoller Sensorik und industrieller Automatisierung.

Neben der Schaltungsentwicklung und Fertigung steht bei den analogen BI-Chips ein ganzheitliches Verständnis der Signalverarbeitung im Gesamtsystem im Mittelpunkt. Modernste Systemsimulationen und parametrische Tests ermöglichen es, komplexe Wechselwirkungen im analogen und Mixed-Signal-Design frühzeitig zu erkennen und gezielt zu optimieren. Dadurch wird eine hohe Zuverlässigkeit und Präzision der Chips gewährleistet – Eigenschaften, die in sicherheitskritischen Anwendungen unverzichtbar sind.

Wesentliche Merkmale der analogen Chips am Barkhausen Institut:

- Hochfrequenzoptimiertes Mixed-Signal-Design inkl. innovativen Antennenkonzepten

- Ganzheitliche Systemsimulationen für präzise Fehlererkennung und -optimierung

- Fertigung in modernsten Halbleitertechnologien im Silicon Saxony-Cluster

- Maßgeschneiderte Gehäusepakete und Leiterplatten für optimale Hochfrequenzkommunikation

- Umfangreiche Charakterisierung und Funktionsmessungen im hauseigenen Labor

- Entwicklung von Chips für spezialisierte Anwendungen wie Joint Communications & Sensing sowie Computertomographie

- Einsatz in sicherheitskritischer Kommunikation, komplexer Sensorik und Industrieautomation

- Enge Verzahnung von Hochfrequenz-/Analog-Designs mit digitalen Plattformchips für synergetische Lösungen

Tapeouts der analogen und Mixed-Signal Funkchips am Barkhausen Institut

TPO1 (2020)

- Erste Grundbausteine

- Einrichtung des Design-Flows

- LNA, VCO, PA, Transformatorblöcke bei 26 und 60 GHz

TPO2 (2021)

- Zweite Generation von Grundbausteinen

- On-Chip De-Embedding Strukturen

- VCOs, Power Detector, LNAs, passive Strukturen bei 26 und 60 GHz

TPO3 (2022)

- Rekonfigurierbare LNAs für 6G Anwendungen

- Aktiver RFID Tag bei 60 GHz

- On-Chip Antenne bei 60 GHz

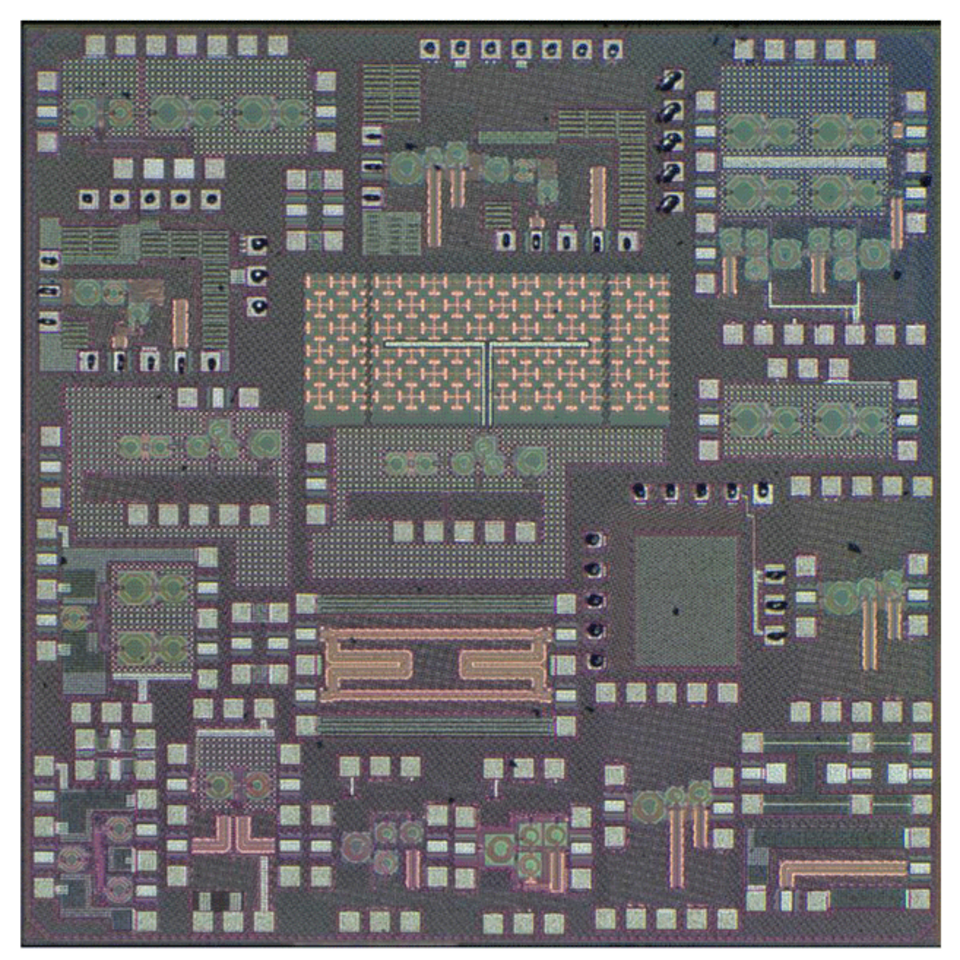

TPO4 (2023)

- Vollständige Sender und Empfangsblöcke bei 26 GHz

- PAs und LNAs bei 26, 60 und 77 GHz

- Elektrisch symmetrischer Duplexer für Full-Duplex Anwendungen im FR2 Band

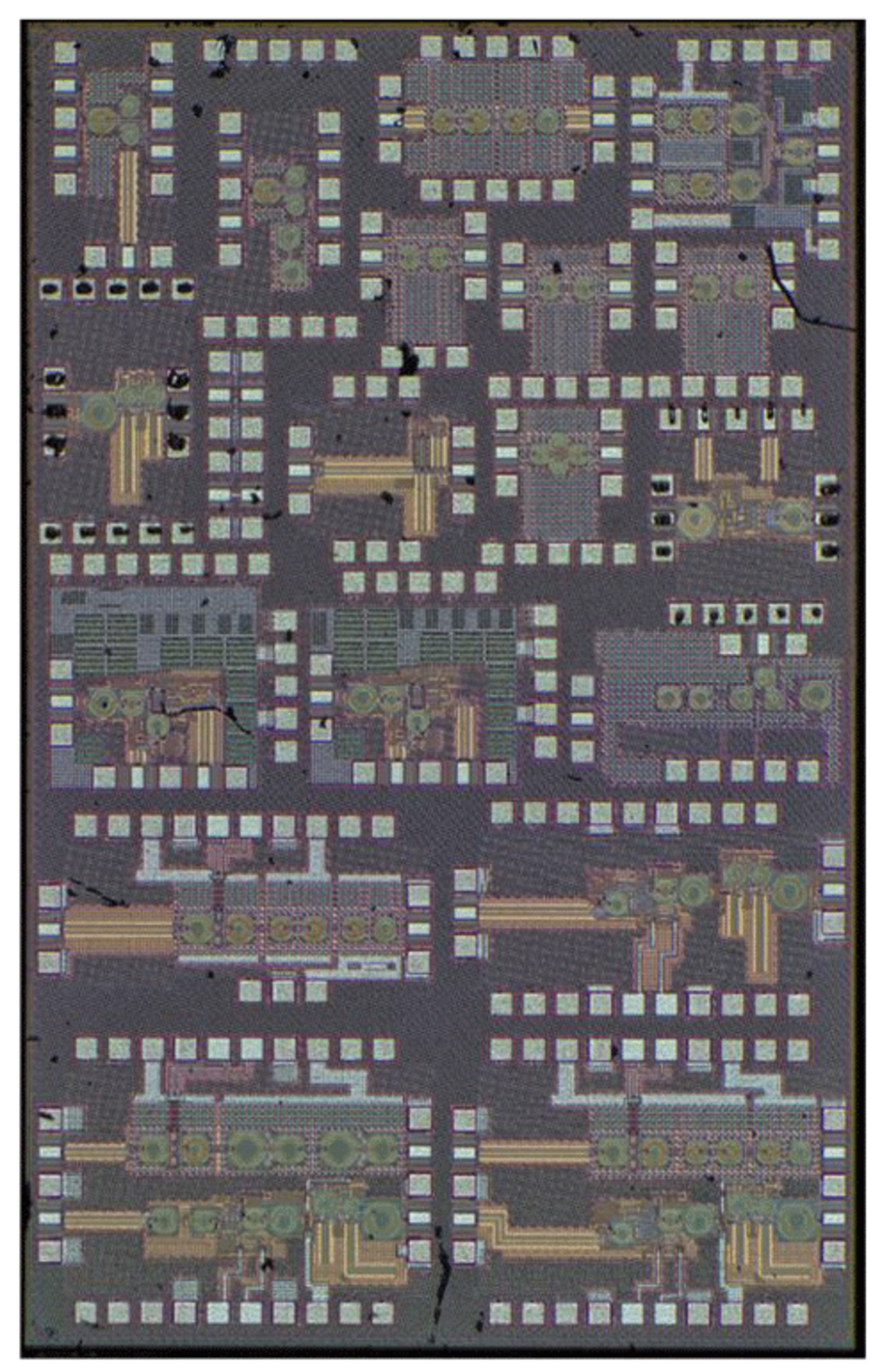

TPO5 (2024)

- Grundbausteine für Computertomographieanwendungen

- OOK-Sender bei 60 GHz

- Mixer-First Empfänger bei 60 GHz

TPO6 (2025)

- JTAG Schnittstelle

- Full-Duplex Transceiver bei 26 GHz

- IQ-Empfänger bei 26 GHz

- Mixer-First Empfänger bei 26 GHz

TPO7 (Anfang 2026, geplant)

- Multi-Band Empfänger

- Full-Duplex Transceiver mit Analog/RF Selbstinterferenzunterdrückung (SIC) bei 26 GHz

- Adaptiver Sender und Empfänger für FR3 Bänder

- IQ-Transceiver bei 26 GHz

TPO8 (2026, geplant)

- Integration eines Third-Party DAC/ADC in bestehenden RF-Transceiver im FR3-Band

- Machbarkeitsstudie zur Integration einer vollständigen Basisbandlösung in Masur‑Chips

Lehre

Joint Communication and Sensing RF Hardware (EuI-NES-E-HJCAS)

Dieses Modul vermittelt die Grundlagen des Hardware-Systemdesigns für kombinierte Kommunikations- und (Radar-)Sensinganwendungen. Es behandelt Details zu RF-Front-End-Komponenten sowie verschiedene Antennenoptionen im Kontext der Systementwicklung. Darüber hinaus werden aktuelle Forschungsarbeiten in diesem Bereich vorgestellt, die zu einem vertieften Verständnis von Hardware-Design und messtechnischer Charakterisierung für zukünftige Anwendungen auf Basis von Key Performance Indicators (KPIs) führen.

Dozent: Dr. Padmanava Sen, Kursbetreuer: Prof. Dr. Gerhard Fettweis

Physical Design (English only)

Physical design is an integral part of development of digital hardware. The content taught in this course will help the students to plan and execute implementations of systems like processors, advanced VLSI systems design and physical layers of communications.